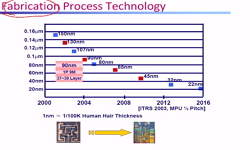

공정기술과 EDA 툴의 발전에 따라서 하나의 실리콘 다이(Die)에 많은 IP가 집적되고 멀티프로세서가 포함되는 SoC 구조가 가능해지고 있다 그러나 대부분의 기존 SoC 버스는 공유버스 구조라는 ...

http://chineseinput.net/에서 pinyin(병음)방식으로 중국어를 변환할 수 있습니다.

변환된 중국어를 복사하여 사용하시면 됩니다.

- 中文 을 입력하시려면 zhongwen을 입력하시고 space를누르시면됩니다.

- 北京 을 입력하시려면 beijing을 입력하시고 space를 누르시면 됩니다.

효율적인 다중 채널 On-Chip-Bus를 위한 SoC Network Architecture = SoC Network Architecture for Efficient Multi-Channel On-Chip-Bus

한글로보기https://www.riss.kr/link?id=A105641430

-

저자

이상헌 ; 이찬호 ; 이혁재 ; Lee Sanghun ; Lee Chanho ; Lee Hyuk-Jae

- 발행기관

- 학술지명

- 권호사항

-

발행연도

2005

-

작성언어

Korean

- 주제어

-

등재정보

구)KCI등재(통합)

-

자료형태

학술저널

- 발행기관 URL

-

수록면

65-72(8쪽)

- 제공처

- 소장기관

-

0

상세조회 -

0

다운로드

부가정보

국문 초록 (Abstract)

공정기술과 EDA 툴의 발전에 따라서 하나의 실리콘 다이(Die)에 많은 IP가 집적되고 멀티프로세서가 포함되는 SoC 구조가 가능해지고 있다 그러나 대부분의 기존 SoC 버스는 공유버스 구조라는 문제점으로 인해 통신의 병목현상이 발생하고 이는 전체 시스템 성능을 저하시키는 요인이 된다. 많은 경우에 멀티프로세서 시스템의 성능은 CPU 자체의 속도보다는 효율적인 통신과 균형있는 연산의 분배가 좌우하게 된다 따라서 충분한 SoC 버스 대역폭(Bandwidth)을 확보하기 위한 하나의 해결책으로 크로스바 라우터(Crossbar Router)를 이용하여 효율적인 온 칩 버스구조인 SoC Network Architecture(SNA)를 제안한다. 제안된 SNA구조는 다중 마스터(multi-master)에 대해 다중 채널(multi-channel)을 제공하여 통신의 병목현상을 크게 줄일 수 있으며 뛰어난 확장성을 지원한다. 제안된 구조에 따라 모델 시스템을 설계하고 시뮬레이션을 진행한 결과 AMBA AHB 버스에 비해 평균 $40\%$ 이상 효율이 증가했다.

다국어 초록 (Multilingual Abstract)

We can integrate more IP blocks on a silicon die as the development of fabrication technologies and EDA tools. Consequently, we can design complicated SoC architecture including multi-processors. However, most of existing SoC buses have bottleneck in ...

We can integrate more IP blocks on a silicon die as the development of fabrication technologies and EDA tools. Consequently, we can design complicated SoC architecture including multi-processors. However, most of existing SoC buses have bottleneck in on-chip communication because of shared bus architectures, which result in the performance degradation of systems. In most cases, the performance of a multi-processor system is determined by efficient on-chip communication and the well-balanced distribution of computation rather than the performance of the processors. We propose an efficient SoC Network Architecture(SNA) using crossbar routers which provide a solution to ensure enough communication bandwidth. The SNA can significantly reduce the bottleneck of on-chip communication by providing multi-channels for multi-masters. According to the proposed architecture, we design a model system for the SNA. The proposed architecture has a better efficiency by $40\%$ than the AMBA AHB according to a simulation result.

동일학술지(권/호) 다른 논문

-

SRAM 이중-포트를 위한 내장된 메모리 BIST IP 자동생성 시스템 개발

- 대한전자공학회

- 심은성

- 2005

- 구)KCI등재(통합)

-

저전력 테스트를 고려한 효율적인 테스트 데이터 압축 방법

- 대한전자공학회

- 전성훈

- 2005

- 구)KCI등재(통합)

-

- 대한전자공학회

- 김형철

- 2005

- 구)KCI등재(통합)

-

고장 모델 기반 메모리 BIST 회로 생성 시스템 설계

- 대한전자공학회

- 이정민

- 2005

- 구)KCI등재(통합)

ScienceON

ScienceON