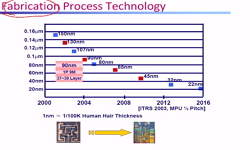

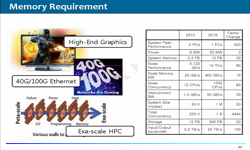

집적회로의 공정기술 및 설계기술이 발전함에 따라 많은 IP가 하나의 반도체 칩에 집적되어 하나의 시스템을 구성하는 SoC 설계가 많이 이루어지고 있다. 본 논문에서는 다양한 IP 간에 효율...

http://chineseinput.net/에서 pinyin(병음)방식으로 중국어를 변환할 수 있습니다.

변환된 중국어를 복사하여 사용하시면 됩니다.

- 中文 을 입력하시려면 zhongwen을 입력하시고 space를누르시면됩니다.

- 北京 을 입력하시려면 beijing을 입력하시고 space를 누르시면 됩니다.

https://www.riss.kr/link?id=A101123711

-

저자

김규철 (단국대학교) ; 서병현 (단국대학교) ; Kim, Kyu-Chull ; Seo, Byung-Hyun

- 발행기관

- 학술지명

- 권호사항

-

발행연도

2009

-

작성언어

Korean

- 주제어

-

등재정보

KCI등재

-

자료형태

학술저널

-

수록면

101-107(7쪽)

-

KCI 피인용횟수

0

- 제공처

-

0

상세조회 -

0

다운로드

부가정보

국문 초록 (Abstract)

집적회로의 공정기술 및 설계기술이 발전함에 따라 많은 IP가 하나의 반도체 칩에 집적되어 하나의 시스템을 구성하는 SoC 설계가 많이 이루어지고 있다. 본 논문에서는 다양한 IP 간에 효율적인 데이터 통신이 이루어지도록 버스 상의 전송 특성에 따라 버스모드를 동적으로 재구성하는 SoC 3중 버스 구조를 제안한다. 제안된 버스는 다중-단일버스 모드, 단일-다중버스 모드로 재구성이 가능하며 따라서 단일버스 모드와 다중버스 모드의 장점을 모두 갖는다. 실험결과 제안된 버스구조는 기존의 고정된 버스구조보다 독립적이며 데이터 전송시간을 단축시킬 수 있음을 확인하였다. 그리고 제안된 버스구조를 JPEG 시스템에 적용한 결과 다중버스구조보다 평균 22%의 전송시간 단축을 얻을 수 있었다.

다국어 초록 (Multilingual Abstract)

Growth in the VLSI process and design technology is resulting into a continuous increase in the number of IPs on a chip to form a system. Because of many IPs on a single chip, efficient communication between IPs is essential. We propose a dynamically ...

Growth in the VLSI process and design technology is resulting into a continuous increase in the number of IPs on a chip to form a system. Because of many IPs on a single chip, efficient communication between IPs is essential. We propose a dynamically reconfigurable 3-layer bus structure which can adapt to the pattern of data transmission to achieve an efficient data communication between various IPs. The proposed 3-layer bus can be reconfigured to multi-single bus mode, and single-multi bus mode, thus providing the benefits of both single-bus and multi-bus modes. Experimental results show that the flexibility of the proposed bus structure can reduce data transmission time compared to the conventional fixed bus structure. We incorporated the proposed bus structure in a JPEG system and verified that the proposed structure achieved an average of 22% improvement in time over the conventional fixed bus structure.

참고문헌 (Reference)

1 서병현, "동적 재구성이 가능한 고성능 시스템온칩 버스 구조에 관한 연구" 369-370, 2007

2 공민철, "다중 마스터 설계를 이용한 AMBA 인터페이스 구현" 한국산업기술대학 2004

3 ALTERA, "multi_master_reference_design" 2002

4 천재익, "SoC를 위한 통신망 설계 동향" 30 (30): 992-1001, 2003

5 조신형, "SoC 플랫폼에서 다층구조 공유버스의 레이턴시 모델과 해석" 13 (13): 85-92, 2005

6 ARM, "Multi-layer AHB Overview" 2001

7 IDEC, "IDEC NEWSLETTER" 2007

8 S. Pasricha, "Fast Exploration of Bus-based On-chip Communication Architectures" 2004

9 K. Sekar, "FLEXBUS : a high-performance system-on-chip communication architecture with a dynamically configurable topology" 571-574, 2005

10 K. Larhiri, "Design of High Performance System-on-Chips Using Communication Architecture Tuners" 23 : 919-932, 2004

1 서병현, "동적 재구성이 가능한 고성능 시스템온칩 버스 구조에 관한 연구" 369-370, 2007

2 공민철, "다중 마스터 설계를 이용한 AMBA 인터페이스 구현" 한국산업기술대학 2004

3 ALTERA, "multi_master_reference_design" 2002

4 천재익, "SoC를 위한 통신망 설계 동향" 30 (30): 992-1001, 2003

5 조신형, "SoC 플랫폼에서 다층구조 공유버스의 레이턴시 모델과 해석" 13 (13): 85-92, 2005

6 ARM, "Multi-layer AHB Overview" 2001

7 IDEC, "IDEC NEWSLETTER" 2007

8 S. Pasricha, "Fast Exploration of Bus-based On-chip Communication Architectures" 2004

9 K. Sekar, "FLEXBUS : a high-performance system-on-chip communication architecture with a dynamically configurable topology" 571-574, 2005

10 K. Larhiri, "Design of High Performance System-on-Chips Using Communication Architecture Tuners" 23 : 919-932, 2004

11 S. Han, "An Efficient Scalable and Flexible Data Transfer Architecture for Multiprocessor SoC with Massive Distributed Memory" 370-371, 2004

12 Kyeong Keol Ryu, "A comparison of five different multiprocessor SoC bus architectures" 202-209, 2001

13 T. Meyerowitz, "A Tool for Describing and Evaluating Hierarchical Real-Time Bus Scheduling Policies" 312-317, 2003

14 Baruch Halachmi, "A MULTI-BUS INTERCONNECTION MODEL" 1138-1142, 1993

동일학술지(권/호) 다른 논문

-

- 한국전기전자학회

- 박준은

- 2009

- KCI등재

-

- 한국전기전자학회

- 박현희

- 2009

- KCI등재

-

예측 지역 목표와 분산 퍼지 제어를 이용한 미지 환경에서의 센서 기반 경로 계획 및 장애물 회피

- 한국전기전자학회

- 곽환주

- 2009

- KCI등재

-

음악 추천을 위한 감정 전이 모델 기반의 음악 분류 기법

- 한국전기전자학회

- 한병준

- 2009

- KCI등재

분석정보

인용정보 인용지수 설명보기

학술지 이력

| 연월일 | 이력구분 | 이력상세 | 등재구분 |

|---|---|---|---|

| 2024 | 평가예정 | 재인증평가 신청대상 (재인증) | |

| 2021-01-01 | 평가 | 등재학술지 선정 (계속평가) |  |

| 2020-12-01 | 평가 | 등재후보로 하락 (재인증) |  |

| 2017-01-01 | 평가 | 등재학술지 선정 (계속평가) |  |

| 2016-01-01 | 평가 | 등재후보학술지 유지 (계속평가) |  |

| 2015-12-01 | 평가 | 등재후보로 하락 (기타) |  |

| 2011-01-01 | 평가 | 등재 1차 FAIL (등재유지) |  |

| 2009-01-01 | 평가 | 등재학술지 유지 (등재유지) |  |

| 2006-01-01 | 평가 | 등재학술지 선정 (등재후보2차) |  |

| 2005-10-17 | 학술지명변경 | 외국어명 : 미등록 -> Journal of IKEEE |  |

| 2005-05-30 | 학술지등록 | 한글명 : 전기전자학회논문지외국어명 : 미등록 |  |

| 2005-03-25 | 학회명변경 | 한글명 : (사) 한국전기전자학회 -> 한국전기전자학회영문명 : 미등록 -> Institute of Korean Electrical and Electronics Engineers |  |

| 2005-01-01 | 평가 | 등재후보 1차 PASS (등재후보1차) |  |

| 2004-01-01 | 평가 | 등재후보 1차 FAIL (등재후보1차) |  |

| 2003-01-01 | 평가 | 등재후보학술지 선정 (신규평가) |  |

학술지 인용정보

| 기준연도 | WOS-KCI 통합IF(2년) | KCIF(2년) | KCIF(3년) |

|---|---|---|---|

| 2016 | 0.3 | 0.3 | 0.29 |

| KCIF(4년) | KCIF(5년) | 중심성지수(3년) | 즉시성지수 |

| 0.24 | 0.22 | 0.262 | 0.17 |

ScienceON

ScienceON DBpia

DBpia